ASIC-Frontend Entwicklung

Verifikations- und Prototyping-Dienste für kundenspezifisches ASIC-Design

Promwad unterstützt Sie bei der Entwicklung eines maßgeschneiderten ASICs, indem wir die Validierung und das Prototyping nach der logischen Implementierung Ihres anwendungsspezifischen integrierten Schaltkreises übernehmen.

Wenn Sie einen Auftragnehmer für die Verifizierung von Schaltungen, das Testen oder die Entwicklung von Treibern für Ihre ASIC-Lösungen suchen, sind Sie hier richtig. Unser qualifiziertes Team verfügt über umfangreiche Erfahrung in der ASIC-Entwicklung.

Unsere Dienstleistungen

- Modellierung und Simulation von ASIC-Designs mit HDL

- Hardwaresimulation und Verifikation auf Zebu, HAPS oder kundenspezifischen FPGA-Entwicklungskits

- Tests mit CPUs (z. B. RISC-V)

- Virtuelle und hybride Schaltungsemulation (basierend auf Zebu & HAPS)

- Hardware- und Softwarevalidierung

- Softwarebasierte Verifikation (ANSI C)

- Vor- und Nach-Silizium-Validierung

- Entwicklung kundenspezifischer Treiber

- UVM-basierte Pre-Silizium-Tests

Unsere Unterstützung endet nicht hier. Wir können Ihre maßgeschneiderten ASIC-Design-Lösungen in spezifische Geräte und eingebettete Systeme integrieren, mit unseren Embedded-Linux-Entwicklungsdiensten oder unserer Edge-KI-Entwicklung.

Fallstudie: Custom-ASIC- und FPGA-Design

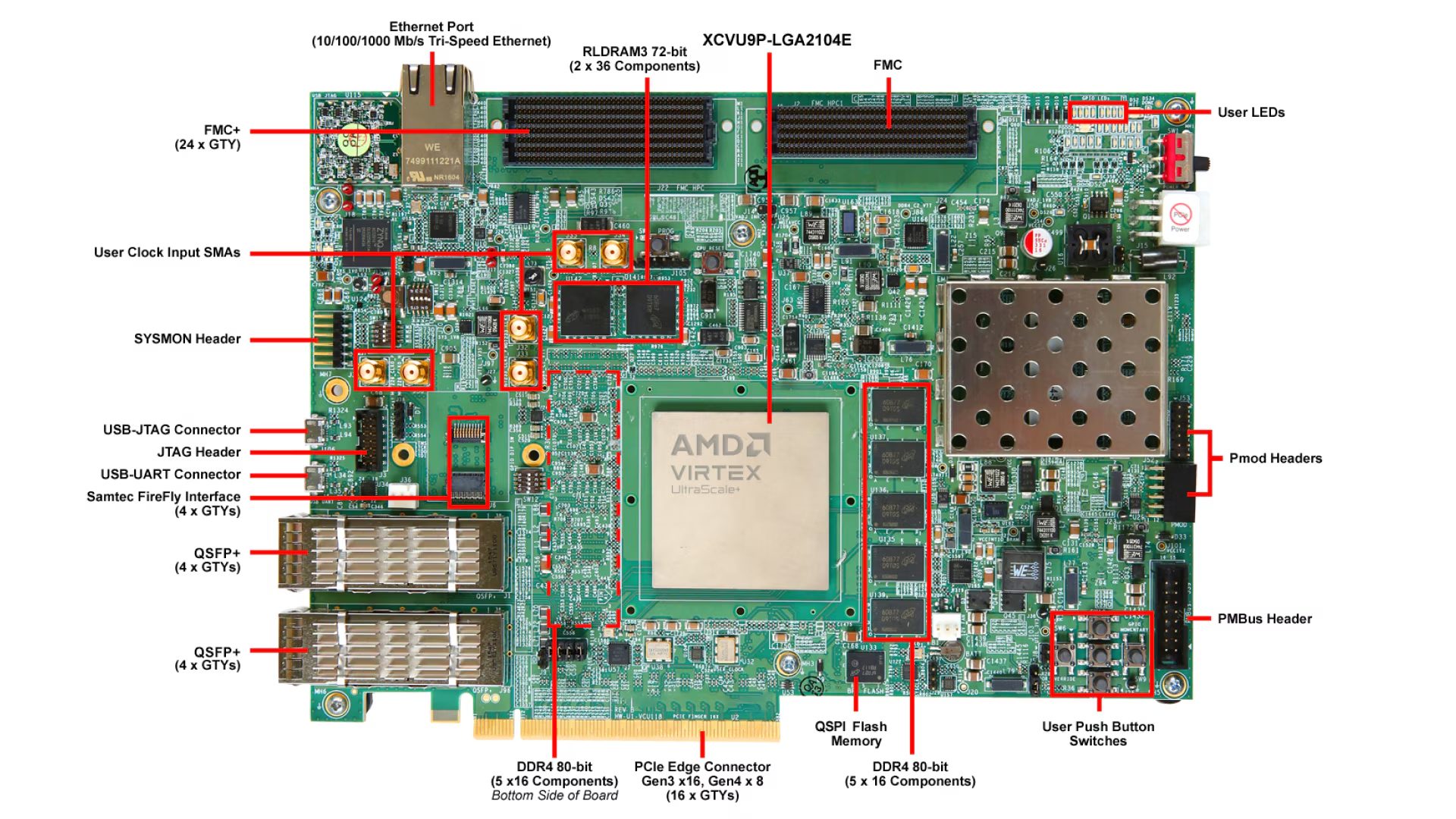

HAPS-80 Prototyping-Lösung von Synopsys

Das Projekt umfasste Test- und Firmware-Design-Dienste für kundenspezifische RISC-V-basierte Schaltungen.

Unsere Teamaufgaben umfassten:

-

BSP und Bare-Metal-Treiber für RISC-V-CPU-Entwicklung

-

Null- und Erststufen-Bootloader

-

Windows-Treiber für PCIe-Endpunkt-Geräteentwicklung (Jungo-Framework)

-

Implementierung von Bring-up-Tests für alle SoC-Komponenten mit Kommunikation über die QSPI-Brücke

-

Simulation auf ZeBu

-

Emulation auf HAPS-80

Unser Team war an der Umsetzung des betreffenden RTL-Designs auf der AMD Virtex™ UltraScale+™ Plattform beteiligt und an der Anbindung von PHYs (Transceiver von AMD und externe PHYs). Wir haben die folgenden von Synopsys entwickelten Blöcke integriert:

-

PCIe Root Complex

-

10G MAC und 10G PCS

-

USB 3.0

Das Prototyping wurde auf den Evaluationskits VCU118 und HTG-960 mit den entsprechenden Mezzanine-Karten durchgeführt. Die Simulation erfolgte in Vivado™ und VCS.

Evaluierungskit VCU118 mit Virtex UltraScale+ FPGA

Die Peripheriekomponenten des entworfenen ASICs

PCIe-Endpunkt, AXI-DMA, GPIO, LPDDR4, UART

QSPI-Brücke

RISC-V

Watchdog-Timer, PVT-Sensor

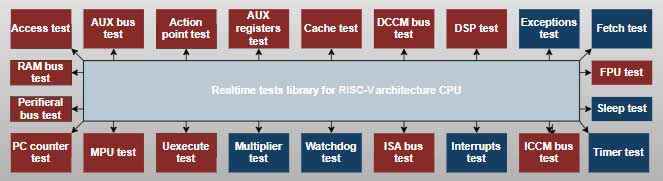

Mikro-Fallstudie zur ASIC-Verification

Unvorhersehbare Auswirkungen deterministischer Erkennung auf CPU und Komponenten

Tags: RISC-V, Test, Echtzeit-Determinismus

Wir haben eine interne Echtzeit-CPU-Testbibliothek entwickelt. Der Test umfasste interne und Peripherie-Busse, interne CPU-Blöcke und mehr. Das Hauptziel bestand darin, Fehler sofort (deterministische Zeit) zu erkennen, die durch jegliche Einwirkung, einschließlich elektromagnetischer Impulse, verursacht wurden.

Wir beschleunigen Ihre Schaltungsentwicklung, indem wir C/ASM-Verifikationssoftware für IP-Blöcke auf Zebu, HAPS oder anderen FPGA-Prototyping-Systemen implementieren.

Unser Technologiestack umfasst, aber ist nicht darauf beschränkt, PCIe-Endpunkt, AXI-DMA, LPDDR4, QSPI und RISC-V (SiFive).

Interessieren Sie sich für ASIC-Verifikation und Prototyping?

Wir werden Sie heute oder am nächsten Werktag kontaktieren. Alle übermittelten Informationen werden vertraulich behandelt.