Entwurf eines SDR-Satellitenmodems für Breitbandverbindungen

Der Kunde

Ein europäisches Unternehmen, das sich auf Software für das Bodensegment der Satellitenkommunikation spezialisiert hat und mit Geräteherstellern und Anbietern von Breitband- und Multimediadiensten zusammenarbeitet.

Die Herausforderung

Entwicklung einer Hardware- und Softwareplattform für ein Satellitenmodem. Der Kunde wollte seine Produktlinie zusätzlich zur ursprünglichen Markenlösung um eine neue Hardwarelösung erweitern.

Die Lösung

Wir haben das Gerät in einem kompakten 1U-Formfaktor entworfen, indem wir es in eine digitale und eine analoge Platine aufgeteilt haben. Dieser Ansatz gewährleistet ein Höchstmaß an Flexibilität: Um die Funktionalität des Geräts zu skalieren, muss nur die analoge Frontend-Platine getauscht werden.

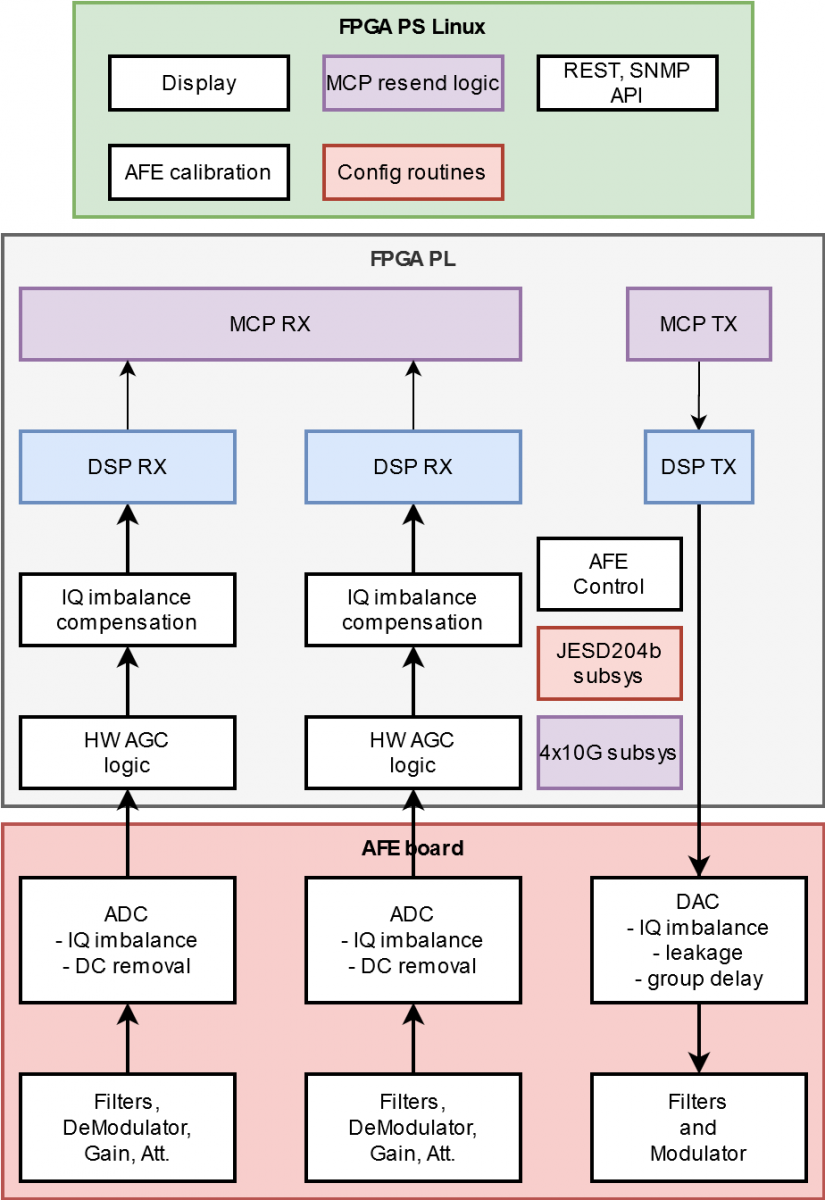

Wir haben uns für Zynq Ultrascale+ als Entwicklungsplattform entschieden. Für die Implementierung der Funktionalität haben wir das Linux-Betriebssystem und programmierbare Logik verwendet.

Unsere Ingenieure haben ein dediziertes Frontend mit Hochgeschwindigkeits-ADC/DAC-Wandlern und modernen Hochfrequenz-Analogmodulatoren/Demodulatoren entwickelt.

Blockdiagramm:

Vier 10G-Schnittstellen und das DPDK-Framework ermöglichen einen Hochgeschwindigkeits-Datenaustausch zwischen Server und Gerät. Die Datenübertragung erfolgt über ein speziell entwickeltes MCP-Protokoll, das eine zuverlässige Datenübertragung über UDP gewährleistet.

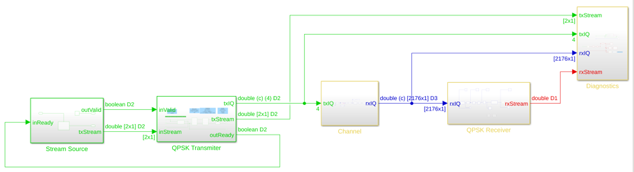

Für die Entwicklung des Modems und der Steuerungssoftware haben wir MATLAB/Simulink verwendet.

Das Systemmodell wurde mittels modellbasiertem Entwurf implementiert, d.h. das Kommunikationssystem wurde vollständig in Simulink mit anschließender HDL-Codegenerierung implementiert. Daraus ergaben sich folgende Vorteile:

- Schneller Entwurf und Verifizierung

- Verarbeitung mehrerer ADC-Abtastwerte pro Taktzyklus (Parallelisierung, Unrolling, Pre-calc)

- Sanfte Umwandlung in einen Festpunkt

- Kanalmodell

- BER-Bewertung in der Entwurfsphase

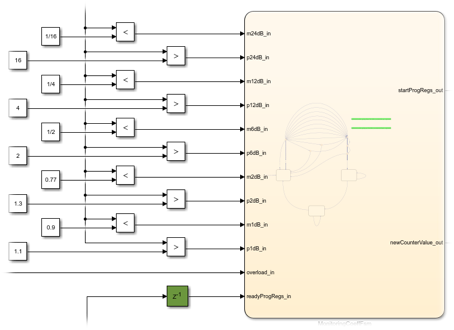

Unsere Ingenieure haben auch neue Ansätze für die AGC-Implementierung und die Kalibierung des analogen Frontends getestet. Wir haben das AGC-Subsystem in Form eines Simulink-Modells implementiert, aus dem der HDL-Code generiert wurde.

- Simulink Stateflow

- HDL-Coder

- AXI4-Lite Write Master-Modell

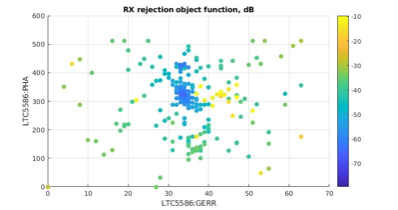

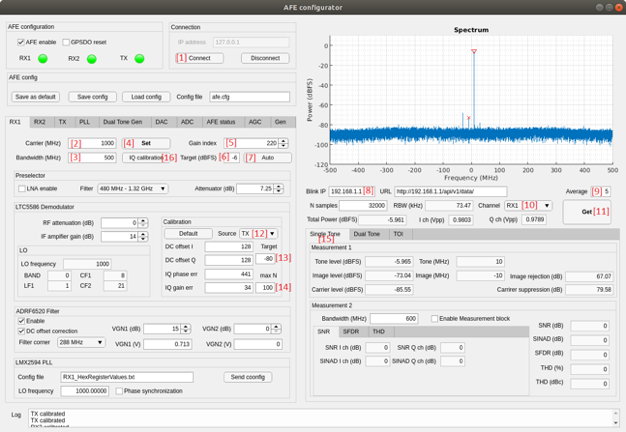

Hardwareblöcke im Demodulator (LTC5586), DAC (DAC37J82) und ADC (ADS54J60) kompensieren die folgenden Effekte:

- IQ-Ungleichgewicht auf dem Empfangsweg

- IQ-Ungleichgewicht in der Übertragungsstrecke

- Trägerunterdrückung

- Gruppenverzögerung

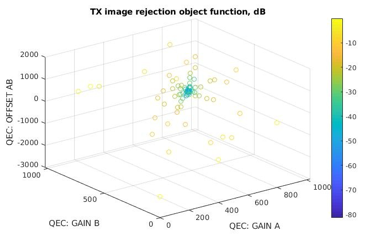

Um die optimalen Parameter für den angegebenen Betriebsmodus zu ermitteln, wurde die Surrogat-basierte Optimierung verwendet. Als Parameterraum dienten Chip-Register. Zielfunktionen waren die Unterdrückung des Spiegelkanals TX & RX und eines Trägerkanals.

Um das Gerät zu konfigurieren und die Signalparameter zu messen, haben wir eine grafische Anwendung entwickelt.

Der Geschäftswert

Der Kunde erhielt ein Satellitenmodem mit folgenden Merkmalen:

- Frequenzbereich: 300 MHz - 2 GHz

- Bandbreite: bis zu 500 MHz

- ZERO-IF-Schema

- Zwei Empfangspfade (ADC 1Gsps) und ein Sendepfad (1xDAC 1,5Gsps)

- 4 х 10G-Ethernet für die Datenübertragung

- Plattform: Zynq Ultrascale+

Unterstützte Betriebsarten:

- Phasenumtastung (PSK), QAM

- Fehlerkorrektur mit LDPC und Faltungscode