Vom Konzept zur Live-PQC-Demo — Drei Unternehmen, eine Plattform

Projekt auf einen Blick: Promwad, Lattice Semiconductor und SEALSQ entwickelten gemeinsam eine Hardwareplattform, die FPGA-Bitstreams mithilfe postquantenkryptografischer Signaturen validiert, und präsentierten diese live auf der Embedded World 2026. Promwad entwickelte eine kundenspezifische Leiterplatte (PCB), die ein Lattice Field-Programmable Gate Array (FPGA) und ein SEALSQ Trusted Platform Module (TPM) auf einer einzigen Platine integriert. Die Plattform blockiert nicht signierte oder manipulierte Firmware auf Hardwareebene — noch bevor sie ausgeführt wird. Die Demo-Plattform richtet sich an Edge-Geräte mit Lebenszyklen von 10 bis 20 Jahren in den Bereichen Robotik, industrielle Automatisierung und kritische Infrastruktur.

Herausforderung

Edge-Geräte mit Lebenszyklen von 10 bis 20 Jahren benötigen Kryptografie, die ebenso lange Bestand hat — doch RSA und ECC werden das Quantenzeitalter nicht überstehen, und Harvest-now-decrypt-later-Angriffe machen dies bereits heute zu einem realen Problem. Gleichzeitig erhöhen der EU Cyber Resilience Act (CRA) und die Radio Equipment Directive (RED) die Anforderungen an Zertifizierungen: Statische Kryptoarchitekturen reichen nicht mehr aus.

Die zentrale Frage lautet daher: Wie verankert man Vertrauen auf Hardwareebene und hält gleichzeitig die kryptografische Ausführung im Feld aktualisierbar? Lattice Semiconductor, SEALSQ und Promwad haben sich zusammengeschlossen, um darauf eine funktionierende Antwort zu entwickeln.

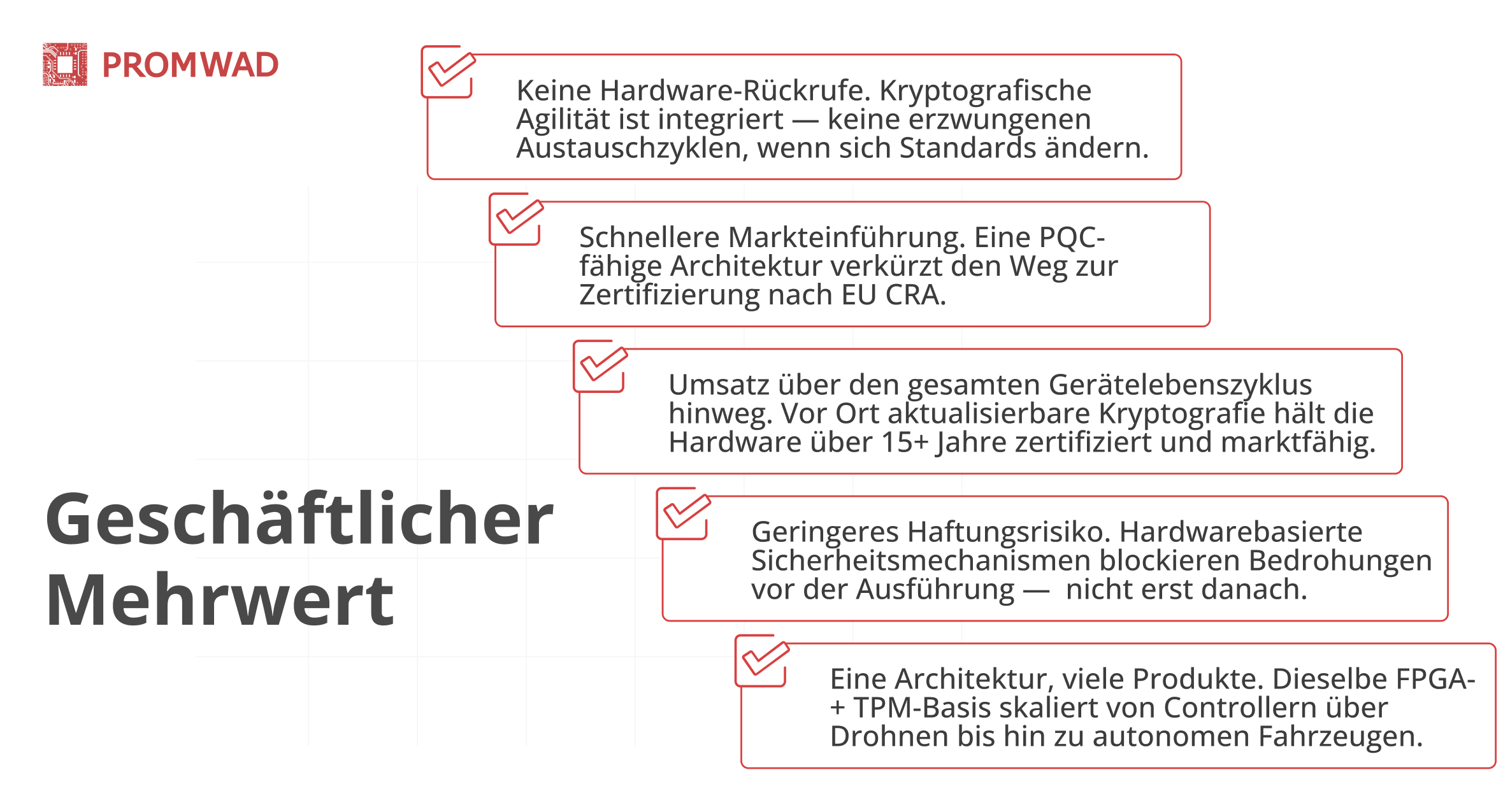

Geschäftlicher Mehrwert

- Keine Hardware-Rückrufe bei geänderten Vorschriften. Geräte mit statischer Kryptografie stehen bei verschärften Standards vor einer schwierigen Entscheidung: Rückruf und Austausch oder Verlust des Marktzugangs. Von Anfang an integrierte kryptografische Agilität beseitigt dieses Risiko vollständig.

- Schnellerer Zugang zu regulierten Märkten. Die Einhaltung des EU CRA wird zunehmend zur Voraussetzung für vernetzte Geräte in Europa. OEMs mit nachgewiesener PQC-Bereitschaft gelangen schneller zur Zertifizierung — und verschaffen sich einen Vorsprung gegenüber Wettbewerbern, die ihre Systeme erst nachträglich anpassen.

- Umsätze über den gesamten Produktlebenszyklus mit derselben Hardware. Ein industrieller Controller mit einer Lebensdauer von 15 Jahren, der im siebten Jahr einen Hardwaretausch benötigt, zerstört die Margen. Vor Ort aktualisierbare Kryptografie hält dieselbe Hardware über die gesamte Einsatzdauer zertifiziert und marktfähig.

- Geringeres Haftungsrisiko. Ein kompromittiertes autonomes System ist nicht nur ein technisches Problem, sondern ein Haftungsfall. Hardwarebasierte Sicherheit, die unterhalb des Betriebssystems arbeitet, verändert die Argumentation von „wir haben es gepatcht“ zu „es wurde vor der Ausführung blockiert“.

- Eine Sicherheitsarchitektur für das gesamte Produktportfolio. Die FPGA- und TPM-Basis ist nicht an eine bestimmte Anwendung gebunden — sie skaliert von industriellen Steuerungen über Drohnen bis hin zu autonomen Fahrzeugen und reduziert dadurch die Sicherheits-Engineering-Kosten pro Produkt mit wachsendem Portfolio.

Lösung

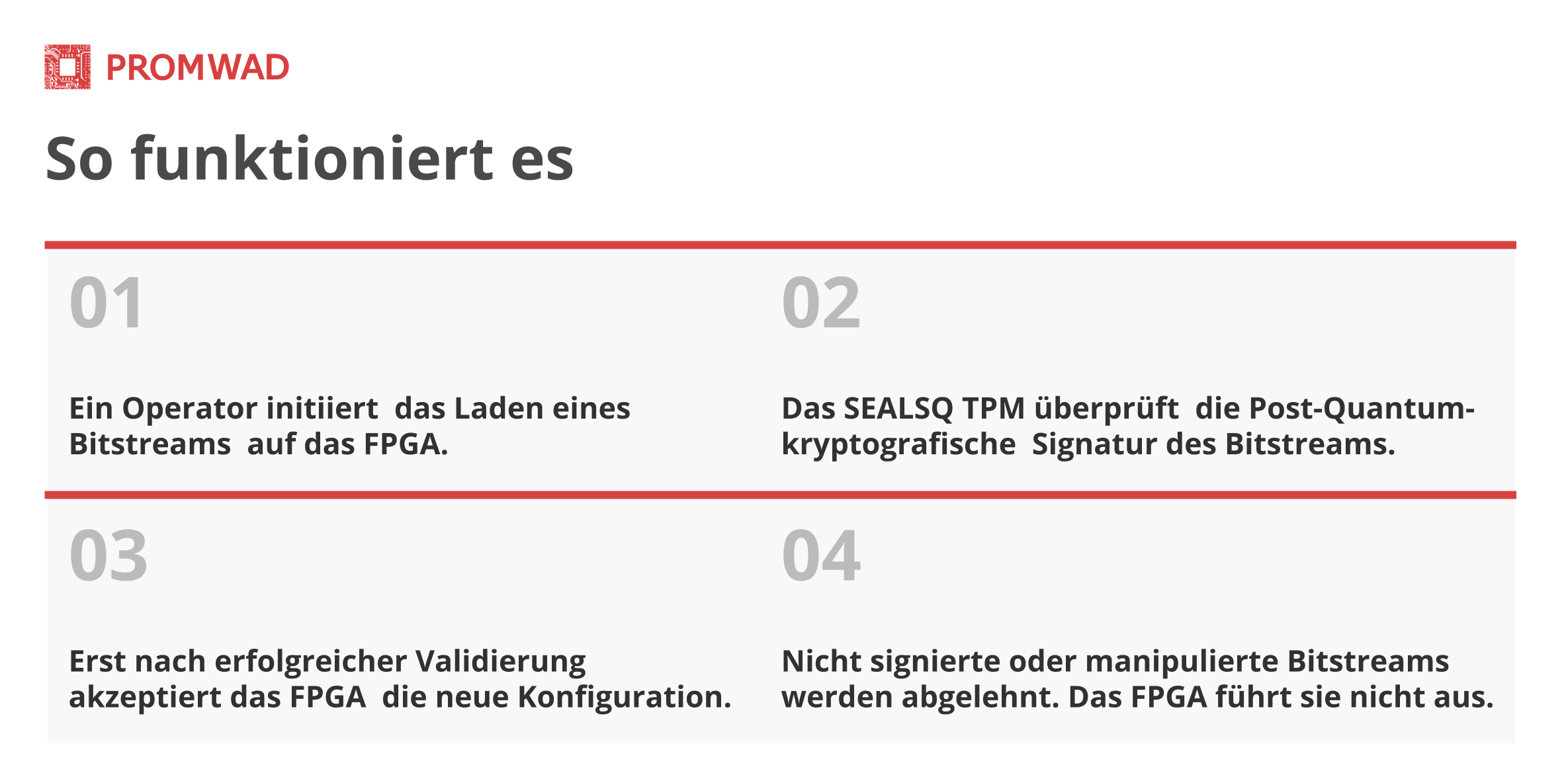

Die drei Partner entwickelten eine Proof-of-Concept-Plattform, die den Vertrauensanker von der kryptografischen Ausführungsebene trennt — und bewiesen ihre Funktionsfähigkeit auf realer Hardware.

Auf der Embedded World 2026 konnten Besucher diesen Prozess in Echtzeit beobachten. Die LED-Anzeige der Platine zeigte unter einem Bitstream eine hexadezimale Zählsequenz (0 bis F). Nachdem ein zweiter Bitstream geladen wurde, validierte das System dessen PQC-Signatur und wechselte anschließend die Anzeige auf ein „DONE“-Muster. Die Demo durchlief mehrere Bitstreams — jeder einzelne wurde vor der Ausführung validiert.

Architektur

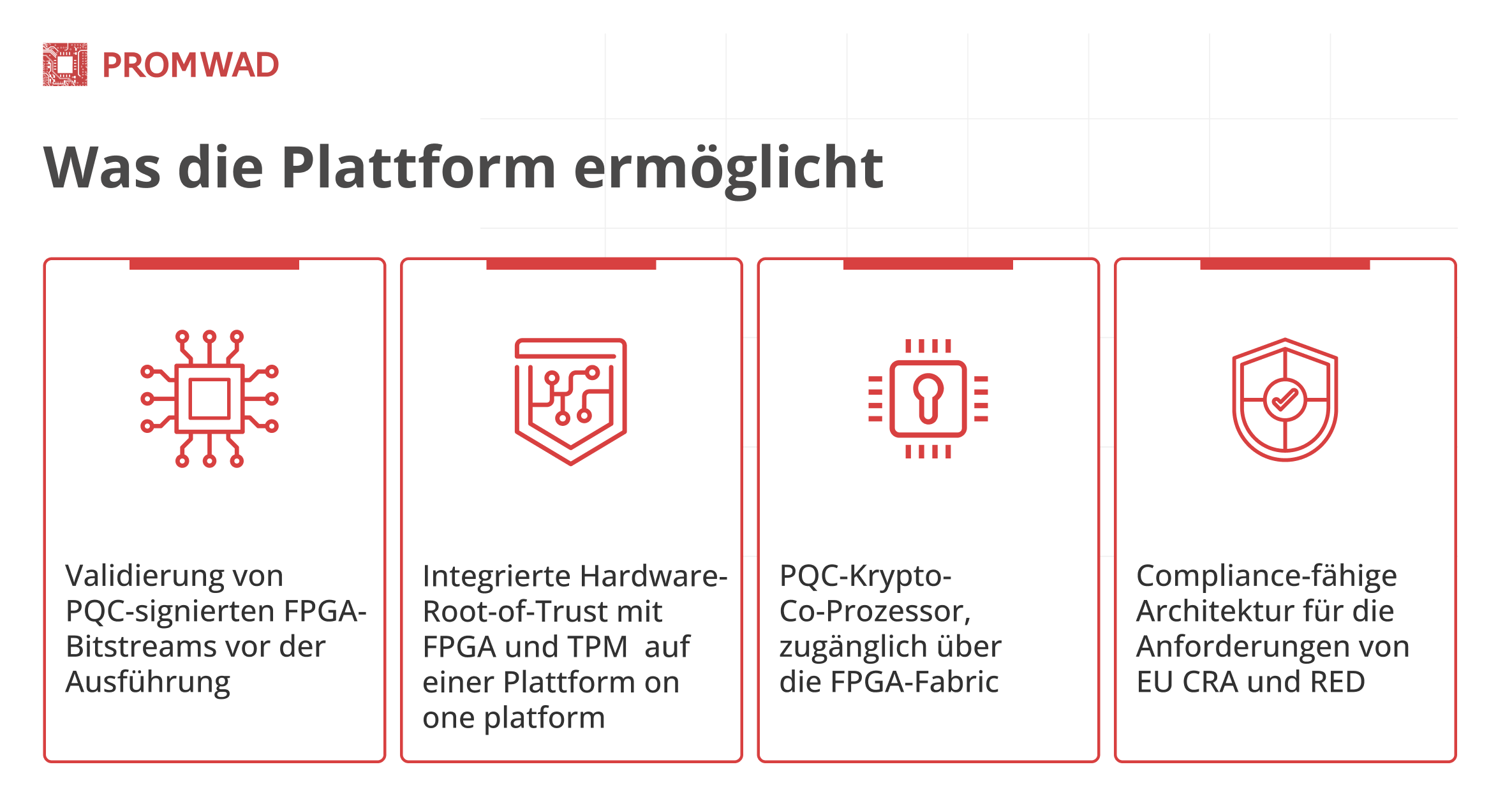

Das SEALSQ QVault TPM + Quantum Shield QS7001 fungiert als unveränderlicher Vertrauensanker. Es speichert Schlüssel, führt Attestierungen durch und verarbeitet PQC-Algorithmen mit Hardwarebeschleunigung. Das TPM ist für die Zertifizierungen CC EAL 5+ und FIPS 140-3 Level 3 ausgelegt. Es verändert sich während der gesamten Lebensdauer des Geräts nicht.

Das Lattice FPGA stellt die anpassungsfähige Ausführungsebene bereit. Es beschleunigt postquantenkryptografische Operationen, unterstützt algorithmische Agilität bei sich weiterentwickelnden Standards und ermöglicht vor Ort aktualisierbare Sicherheitslogik — einschließlich Rollback-Schutz und Anomalie-Filterung.

Promwads kundenspezifische PCB integriert beide Komponenten auf einer einzigen Platine. Promwad übernahm die Schaltplanentwicklung, das PCB-Layout, die Produktionsfreigabe sowie die physische Integration aller Komponenten — und lieferte die Plattform innerhalb eines komprimierten Zeitplans passend zum Termin der Embedded World.

Warum diese Trennung wichtig ist

Ein Gerätehersteller kann kryptografische Algorithmen in bereits ausgelieferten Produkten aktualisieren — ohne die Hardware auszutauschen und ohne den Vertrauensanker zu kompromittieren. Für ein Produkt, das 15–20 Jahre im Einsatz bleiben soll, bedeutet dies den Unterschied zwischen einer einzigen Hardwaregeneration und erzwungener Obsoleszenz.

Ausblick

Dieser Proof of Concept ist der Ausgangspunkt, nicht das Endprodukt. Die Architektur wurde dafür entwickelt, sich zu produktionsreifen Modulen für OEMs skalieren zu lassen, die die nächste Generation von Edge-Geräten entwickeln — von industriellen Steuerungen über autonome Plattformen bis hin zu humanoiden Robotern.

Weitere Leistungen im Bereich FPGA-Design

- FPGA- & SoC-Design-Services: Entdecken Sie unser vollständiges Leistungsspektrum im FPGA-Design — von der RTL-Entwicklung und IP-Core-Integration bis hin zu schlüsselfertigen Embedded-Lösungen.

- FPGA-Architekturdesign für einen Heimstrom-Inverter: Lesen Sie diese Case Study über einen FPGA-Controller auf Basis des Lattice ECP5 für ein Home-Energy-Management-System.

- MCU vs. FPGA: Hardware Root of Trust in der Embedded-Cybersicherheit: Lesen Sie unseren Artikel zum Vergleich von MCU- und FPGA-Ansätzen zur Absicherung eingebetteter Systeme.

FAQ

Decken Sie den gesamten FPGA-Projektumfang ab — von der RTL-Entwicklung bis zur PCB-Integration — oder nur die Firmware-Seite?

Wir decken den gesamten Stack ab: RTL- und IP-Core-Entwicklung, High-Speed-PCB-Design mit DDR4-, JESD204b- und SDI-Schnittstellen, SI/PI- und Thermalsimulationen sowie die Produktionsfreigabe. Unsere Toolchain umfasst Vivado, Quartus Prime und Libero — das bedeutet, dass wir das gesamte FPGA-Subsystem übernehmen können und nicht nur einen Bitstream übergeben.

Sind Sie ein autorisierter Designpartner von Lattice Semiconductor oder arbeiten Sie allgemein mit deren Bausteinen?

Wir sind ein autorisierter Lattice-Designpartner und verfügen über praktische Erfahrung mit den Familien iCE40, MachXO3 und ECP5 — von kompakten Edge-Geräten bis hin zu Steuerungs- und Sicherheitsanwendungen. Dieser Partnerstatus bedeutet priorisierten Zugang zu technischem Support und Ressourcen in frühen Entwicklungsphasen, was bei engen Zeitplänen entscheidend ist. Mehr über unsere Arbeit mit Lattice erfahren Sie hier.

Was bedeutet „End-to-End-FPGA-Design“ in der Praxis — wo beginnt und endet der Leistungsumfang?

Es beginnt mit der Architektur: Bewertung der Projektanforderungen, Auswahl der passenden Plattform und Definition der IP-Core-Struktur. Anschließend folgen RTL-Entwicklung, Integration von IP-Cores, Implementierung von Schnittstellencontrollern und Prozessorkernen sowie die Entwicklung von Datenverarbeitungsalgorithmen. Auf der Hardwareseite umfasst es Schaltplanerstellung, High-Speed-PCB-Layout mit SI/PI- und Thermalanalyse sowie die vollständige Produktionsfreigabe. Der Leistungsumfang endet erst, wenn die Platine auf realer Hardware funktioniert — nicht, wenn die Firmware kompiliert.

Können Sie FPGA in Leistungselektronik-Projekten einsetzen?

Ja. Promwad entwickelt FPGA-basierte Steuerungs- und Signalverarbeitungslösungen für die Leistungselektronik, einschließlich PWM-Algorithmen, Feedback-Regelkreisen, präziser Regelung sowie hardwarebasierter Fehlererkennung für Echtzeitschutz und schnelle Reaktionen.

Können FPGA-basierte Designs im Feld aktualisiert werden, wenn sich Anforderungen oder Standards ändern, ohne dass ein Hardware-Rückruf erforderlich ist?

Das ist einer der zentralen Vorteile von FPGA gegenüber fest verdrahteten Logiklösungen. Die programmierbare Fabric kann mit einem neuen Bitstream neu konfiguriert werden — wodurch sich Algorithmen, Protokolle oder Sicherheitslogik aktualisieren lassen, ohne die physische Hardware zu verändern. Für industrielle Geräte mit langen Lebenszyklen bedeutet das, dass eine einzige Hardwaregeneration konform und funktionsfähig bleiben kann, auch wenn sich Anforderungen weiterentwickeln. Wir berücksichtigen diese Lebenszyklus-Flexibilität bereits in der Architekturphase.